與CMOS製程相容之微機電元件薄膜材料機械性質檢測技術

以微結構之電路行為反算薄膜機械性質技術,過去二十年來最重要之成果主要出自MIT之Prof. Stephen D. Senturia研究室,其技術關鍵是以實驗量測大量不同尺寸之微測試結構,再據以歸納出靜電結構之吸附電壓 (pull-in voltage) 與材料之機械性質的經驗公式,最後由該經驗公式反算薄膜材料之機械性質。此技術之優點是臨界電壓相當容易量測,缺點是必須作大量的實驗量測,且必須配合不同的邊界條件及幾何尺寸,引入許多修正因子,以修正經驗公式,方可得到較準確的結果。本研究團隊近年來著力於開發適用於晶圓級檢測(wafer level testing)的材料機械性質檢測技術,利用CMOS-MEMS testkey的電路行為,量取測試件吸附電壓(pull-in voltage),即可萃取出CMOS製程中金屬薄膜之機械參數。

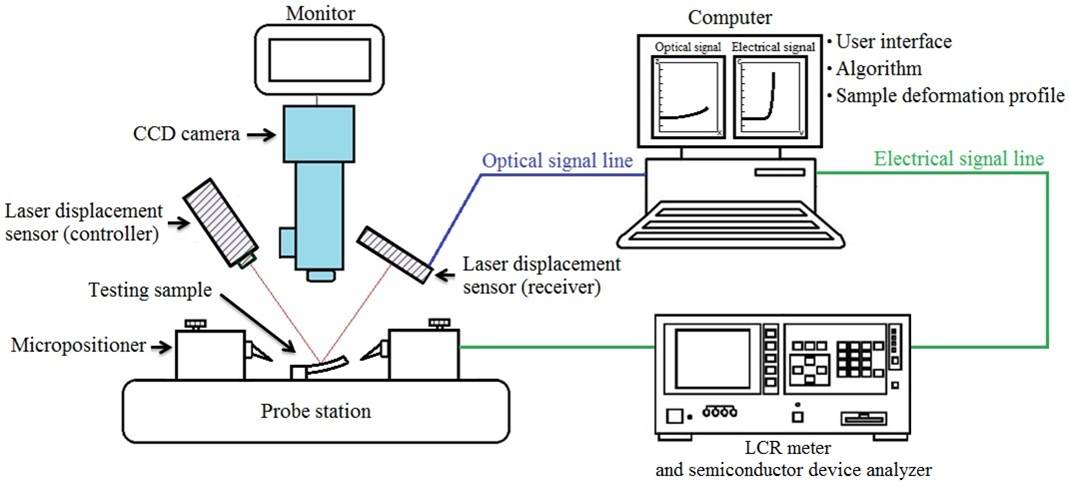

Figure. Development of OptoElectroMechanical(OEM) Wafer-Level Testing System for Thin Film Material of CMOS-MEMS Devices